MiST ZX Spectrum 48K |

|

|

Although I loved the others, too, still ZX Spectrum was my real computer in the 80’s. From the hardware point of view it was a relatively simple machine, comparable to its main competitor, the C64. Spectrum's sound was poor next to the SID chip, the ULA could not draw sprites, the “famous” attribute clash effect was visible everywhere. Who knows why, millions of people loved this machine anyway. I was one of them. I am. |

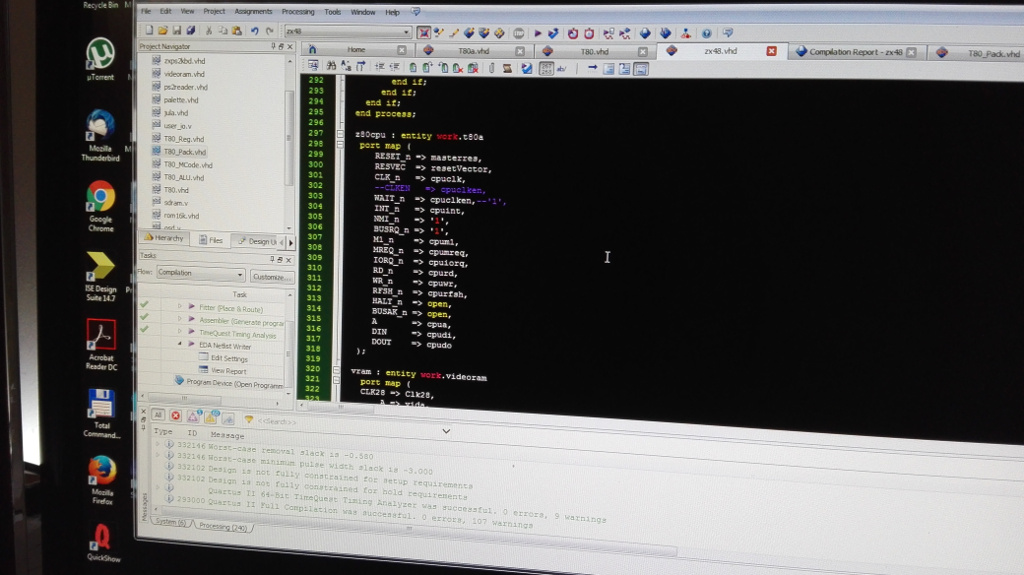

I put these parts together along with the MiST modules (SDRAM controller, OSD display, USERIO and DATAIO modules), so my MiST version started to work.I know that there is a feature-rich version already published for the MiST, but try to understand, I HAD TO create my own. :-)

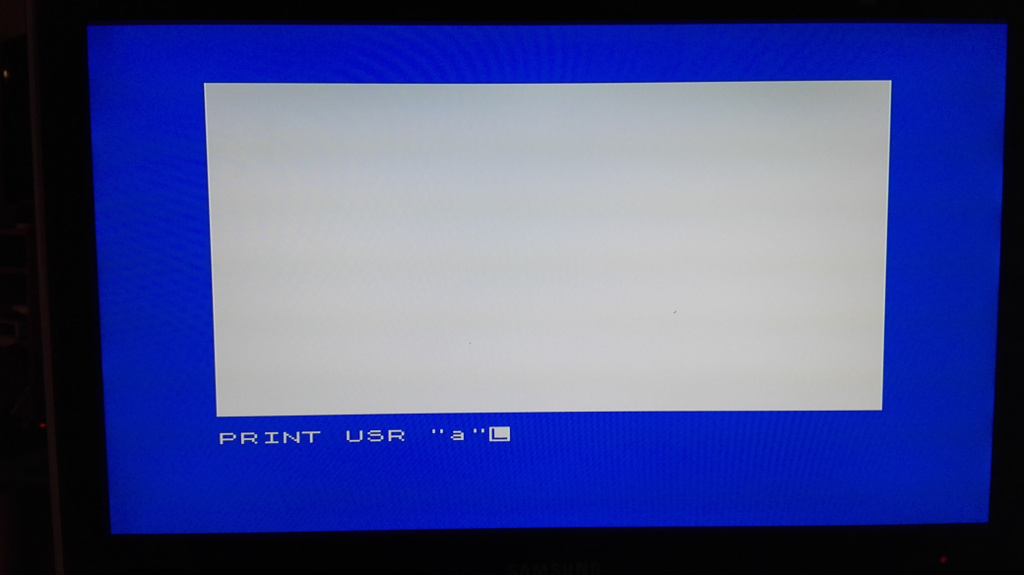

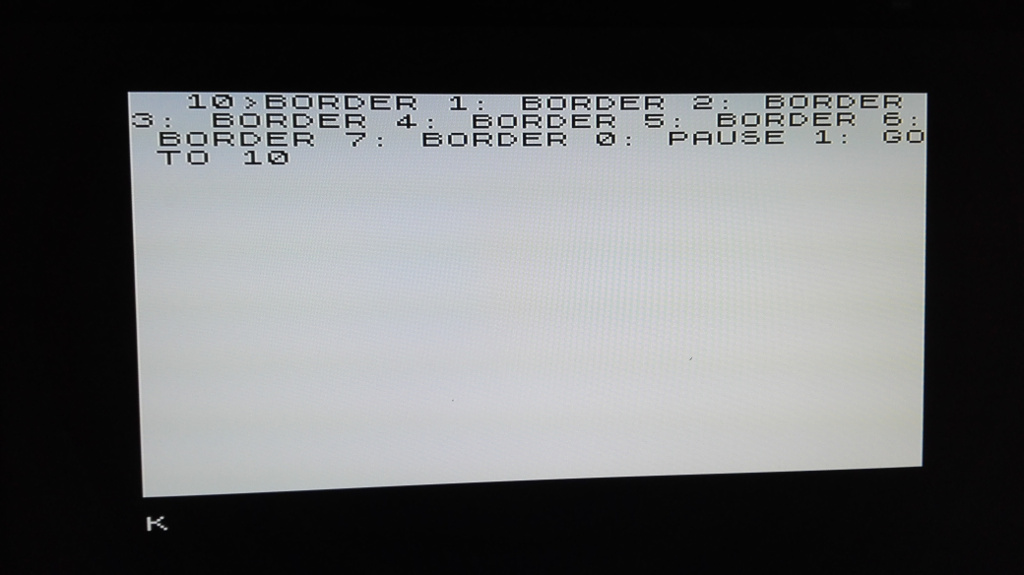

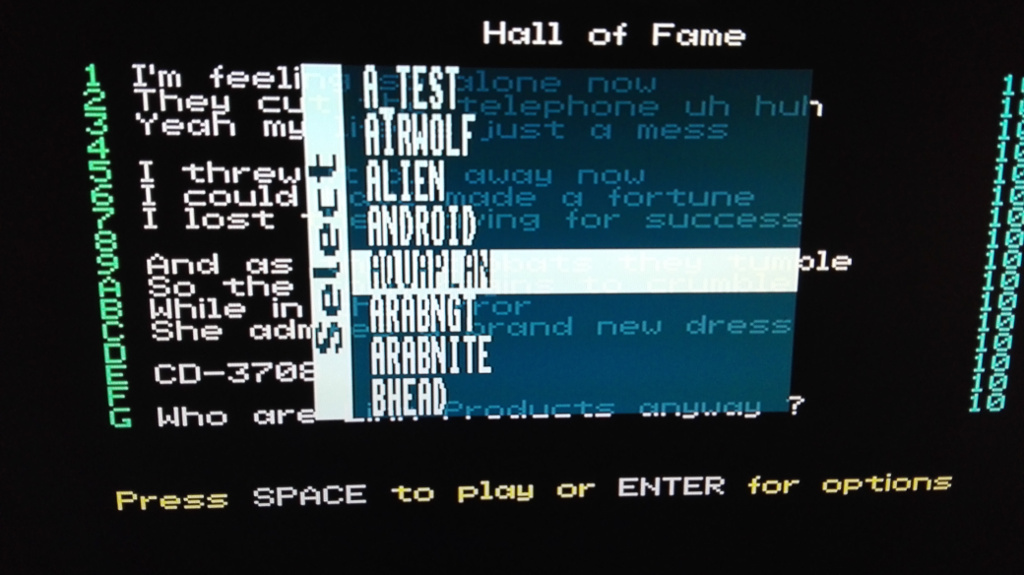

I did not care about extra hardware. All I wanted is a real ZX Spectrum 48K. Now my version can load the widely supported .SNA snapshot files and produce RGB+Sync signals compatible with the PAL video timing. You need a Euro Scart cable for this core. As it uses RGB signals, the picture quality as good as it gets. For loading the .SNA files I had to patch the Spectrum ROM a bit, so the original LOAD routines are replaced with a small Z80 assembly program, that loads the .SNA and execute it.

The hardware also needed some minor changes. In order to load the SNA file, a small RAM space is needed which does not interfere the main RAM area where the snapshot is loading in. For this I opened a small RAM window (16 bytes at $04B0..$04BF) inside the ROM. There was a forgotten ZX81 subroutine called "program name" at the address $04AA, unused by the spectrum. This area is used now by the assembly program placed at the address $0556, where the original LOAD routine seated before. A couple of temporary bytes and the CPU stack is in this window while the snapshot is loading.

The video memory (same way as in my other cores) is inside the FPGA. However contention would not be necessary here, in order to maintain the original timing, it is implemented. The upper 32k of the spectrum memory and the SNA buffer placed in the MiST SDRAM. When the user selects an SNA file on the OSD menu, the hardware loads the entire SNA content into the SDRAM just above the first 64K. Then the SNA loaded gets the bytes from there.

Some extra features will be added to the original hardware. I can't tell why (probably nobody shall use these), just doing it for fun.

- RESET vector for the Z80 CPU, so the RESET can start anywhere in the memory. (This is how snapshots start, already implemented)

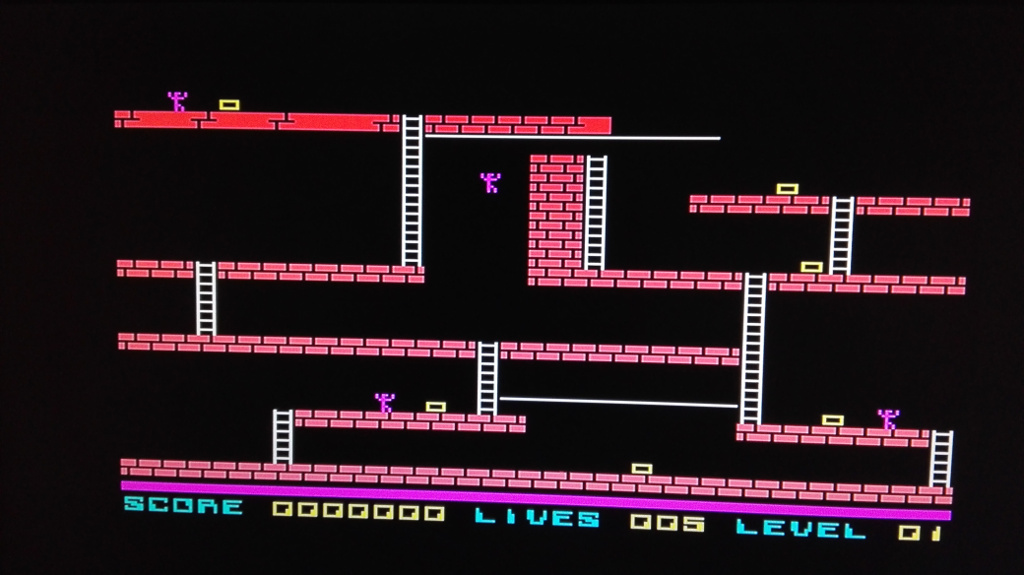

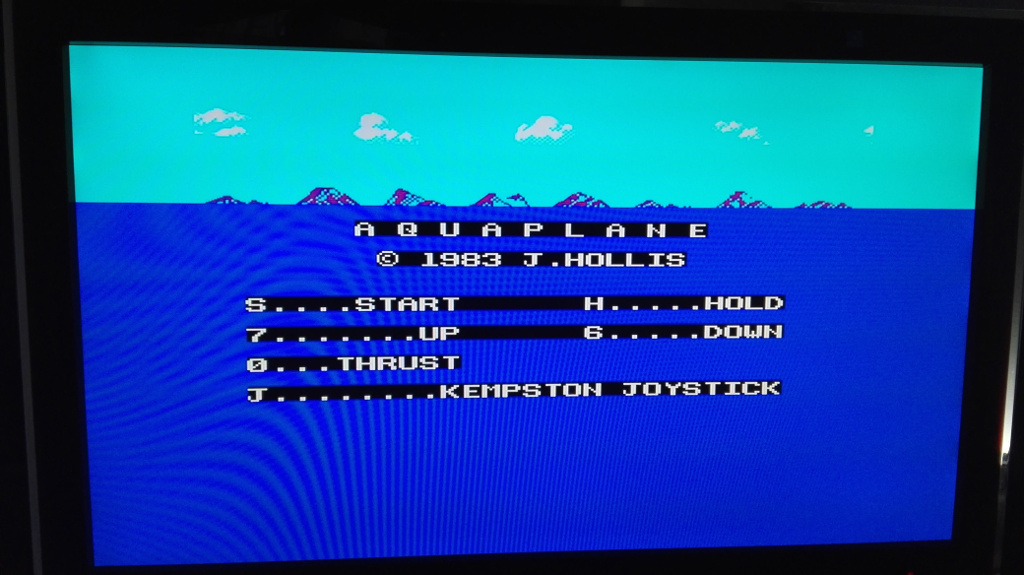

- Kempston joy interface mapped to the 1st digital joy port of the MiST (already implemented)

- Support other joystick types

- RGB palette for the main colors (you can select 16 out of the 4096 available colors)

- Attribute FLASH can be turned on/off, 16 colors can be used for paper and ink independently

- 4th bit for the border, so 16 colors for the border

- Timex compatible video mode (6144 screen bytes plus 6144 attr bytes )

- Screen complete on/off (fullscreen border effects, it this useful at all?)

- Contention effect on/off (speeds up the whole system just a bit)

- Double CPU clock (7MHz)

- More memory pages

Plans for the future:

- Scan doubler for VGA monitors. This module can be added to the ZX48 core and can display 624 VGA scanlines. For monitors that tolerate this, it will be a cycle compatible solution.

- Standard VGA mode spectrum. In this case display 524 scanlines only, so every VGA monitor must accept the video signal. The drawback is that this version will not be cycle compatible with the original ZX Spectrum, since only 262 spectrum scanlines will be drawn instead of 312. Most of the games will run on the core, but special effects (attribute, border) age gonna be wrong as the timing will be different. Also, if something is synchronized to the interrupts, it can be faster. (VGA has a 60Hz refresh rate opposed to the 50Hz of the PAL system)

- ZX Spectrum 128. Once the 48K version works as I expect, I will implement the 128K version too.

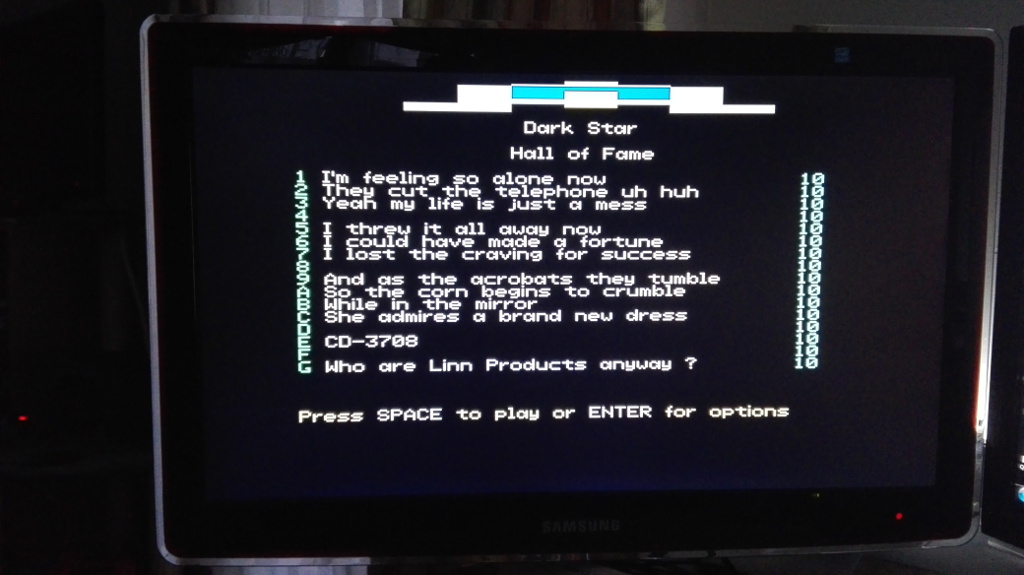

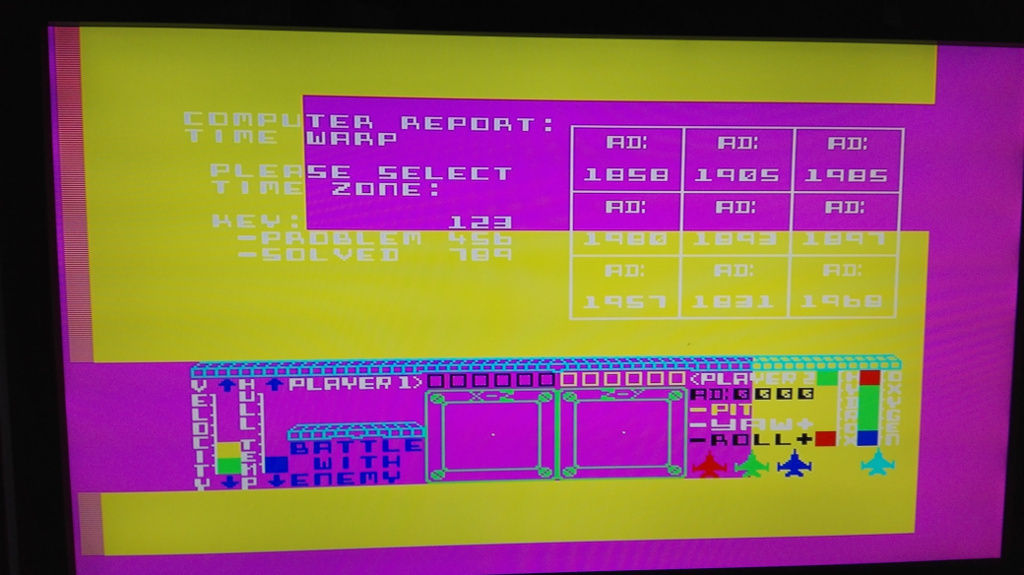

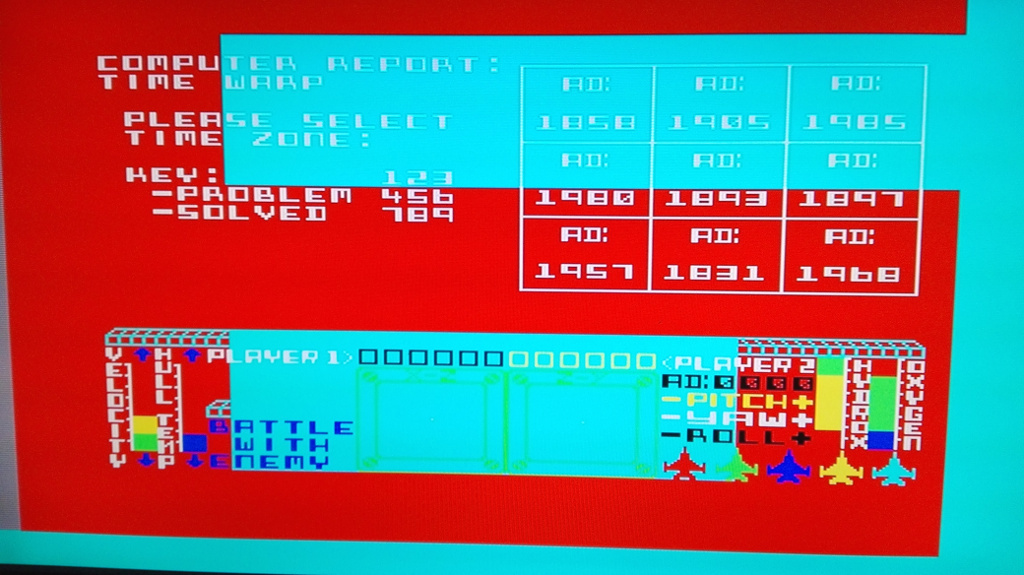

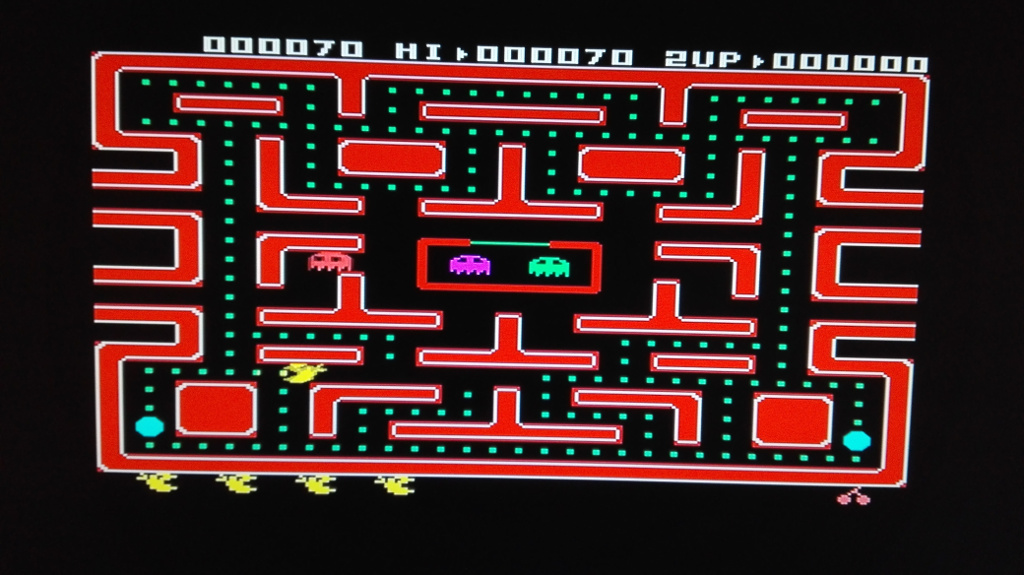

Images:

|

|

In case of a 16K spectrum, this value would be around 32K.

|

|

|

|

|

|

|

|

|

|

Although the full screen numbers look great, the left side of the border effect has some issues.

|

|

|

Downloads:

ZX48.RBF /no VGA support jet, only for Scart cable/

ZX48.ROM

Some games

Thanks to:

- Gábor Orvos, who pushed (and inspired) me to implement this core on the MiST

Links and references:

[Home | FPGA development]